## EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

| 1 | . MOVLW | 03H   |      | Fetch 1 | Execute 1 |           |           |             |              |   |

|---|---------|-------|------|---------|-----------|-----------|-----------|-------------|--------------|---|

| 2 | . MOVWF | GPIO  |      |         | Fetch 2   | Execute 2 |           |             |              |   |

| 3 | CALL    | SUB_1 |      |         |           | Fetch 3   | Execute 3 |             |              |   |

| 4 | BSF     | GPIO, | BIT1 |         |           |           | Fetch 4   | Flush       |              |   |

|   |         |       |      |         |           |           |           | Fetch SUB_1 | Execute SUB_ | 1 |

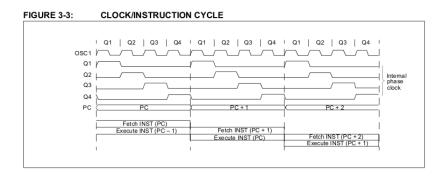

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

TABLE 10-2: INSTRUCTION SET SUMMARY

| Mnemonic, |      | Description                  | Cycles      | 12-    | Bit Opc | Status | Notes    |         |

|-----------|------|------------------------------|-------------|--------|---------|--------|----------|---------|

| Opera     | nds  | Description                  | Ton Cycles  |        |         | LSb    | Affected | Notes   |

| ADDWF     | f, d | Add W and f                  | 1           | 0001   | 11df    | ffff   | C, DC, Z | 1, 2, 4 |

| ANDWF     | f, d | AND W with f                 | 1           | 0001   | 01df    | ffff   | Z        | 2, 4    |

| CLRF      | f    | Clear f                      | 1           | 0000   | 011f    | ffff   | Z        | 4       |

| CLRW      | _    | Clear W                      | 1           | 0000   | 0100    | 0000   | Z        |         |

| COMF      | f, d | Complement f                 | 1           | 0010   | 01df    | ffff   | Z        |         |

| DECF      | f, d | Decrement f                  | 1           | 0000   | 11df    | ffff   | Z        | 2, 4    |

| DECFSZ    | f, d | Decrement f, Skip if 0       | 1(2)        | 0010   | 11df    | ffff   | None     | 2, 4    |

| INCF      | f, d | Increment f                  | 1           | 0010   | 10df    | ffff   | Z        | 2, 4    |

| INCFSZ    | f, d | Increment f, Skip if 0       | 1(2)        | 0011   | 11df    | ffff   | None     | 2, 4    |

| IORWF     | f, d | Inclusive OR W with f        | 1           | 0001   | 00df    | ffff   | Z        | 2, 4    |

| MOVF      | f, d | Move f                       | 1           | 0010   | 00df    | ffff   | Z        | 2, 4    |

| MOVWF     | f    | Move W to f                  | 1           | 0000   | 001f    | ffff   | None     | 1, 4    |

| NOP       | _    | No Operation                 | 1           | 0000   | 0000    | 0000   | None     |         |

| RLF       | f, d | Rotate left f through Carry  | 1           | 0011   | 01df    | ffff   | C        | 2, 4    |

| RRF       | f, d | Rotate right f through Carry | 1           | 0011   | 00df    | ffff   | C        | 2, 4    |

| SUBWF     | f, d | Subtract W from f            | 1           | 0000   | 10df    | ffff   | C, DC, Z | 1, 2, 4 |

| SWAPF     | f, d | Swap f                       | 1           | 0011   | 10df    | ffff   | None     | 2, 4    |

| XORWF     | f, d | Exclusive OR W with f        | 1           | 0001   | 10df    | ffff   | Z        | 2, 4    |

|           |      | BIT-ORIENTED FILE REG        | SISTER OPER | ATIONS | ;       |        |          |         |

| BCF       | f, b | Bit Clear f                  | 1           | 0100   | bbbf    | ffff   | None     | 2, 4    |

| BSF       | f, b | Bit Set f                    | 1           | 0101   | bbbf    | ffff   | None     | 2, 4    |

| BTFSC     | f, b | Bit Test f, Skip if Clear    | 1(2)        | 0110   | bbbf    | ffff   | None     |         |

| BTFSS     | f, b | Bit Test f, Skip if Set      | 1(2)        | 0111   | bbbf    | ffff   | None     |         |

|           |      | LITERAL AND CONT             | ROL OPERATI | ONS    |         |        |          |         |

| ANDLW     | k    | AND literal with W           | 1           | 1110   | kkkk    | kkkk   | Z        |         |

| CALL      | k    | Call Subroutine              | 2           | 1001   | kkkk    | kkkk   | None     | 1       |

| CLRWDT    |      | Clear Watchdog Timer         | 1           | 0000   | 0000    | 0100   | TO, PD   |         |

| GOTO      | k    | Unconditional branch         | 2           | 101k   | kkkk    | kkkk   | None     |         |

| IORLW     | k    | Inclusive OR literal with W  | 1           | 1101   | kkkk    | kkkk   | z        |         |

| MOVLW     | k    | Move literal to W            | 1           | 1100   | kkkk    | kkkk   | None     |         |

| OPTION    | _    | Load OPTION register         | 1           | 0000   | 0000    | 0010   | None     |         |

| RETLW     | k    | Return, place Literal in W   | 2           | 1000   | kkkk    | kkkk   | None     |         |

| SLEEP     | _    | Go into Standby mode         | 1 1         | 0000   | 0000    | 0011   | TO, PD   |         |

| TRIS      | f    | Load TRIS register           | 1           | 0000   | 0000    | Offf   | None     | 3       |

| XORLW     | k    | Exclusive OR literal to W    | 1 1         | 1111   | kkkk    | kkkk   | z        |         |

Note 1: The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. See Section 4.7 "Program Counter".

- 2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

- 3: The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

- 4: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be

# TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                              |

| х             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; $d=0 \text{ (store result in W)}$ $d=1 \text{ (store result in file register '} \text{£'})$ Default is $d=1$                                   |

| label         | Label name                                                                                                                                                         |

| TOS           | Top-of-Stack                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                    |

| WDT           | Watchdog Timer counter                                                                                                                                             |

| TO            | Time-out bit                                                                                                                                                       |

| PD            | Power-down bit                                                                                                                                                     |

| dest          | Destination, either the W register or the specified register file location                                                                                         |

| [ ]           | Options                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                 |

| €             | In the set of                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                |

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

## Byte-oriented file register operations 11 5 4 OPCODE d f (FILE #) d = 0 for destination W d = 1 for destination f f = 5-bit file register address Bit-oriented file register operations 11 5 4 OPCODE b (BIT #) f (FILE #) b = 3-bit address f = 5-bit file register address Literal and control operations (except GOTO) 11 8 7 OPCODE k (literal) k = 8-bit immediate value Literal and control operations - GOTO instruction 11 9 8 OPCODE k (literal) k = 9-bit immediate value

FIGURE 4-3: PIC10F200/204 REGISTER FILE MAP

| File Address |                                 |

|--------------|---------------------------------|

| 00h          | INDF <sup>(1)</sup>             |

| 01h          | TMR0                            |

| 02h          | PCL                             |

| 03h          | STATUS                          |

| 04h          | FSR                             |

| 05h          | OSCCAL                          |

| 06h          | GPIO                            |

| 07h          | CMCON0 <sup>(2)</sup>           |

| 08h<br>0Fh   | Unimplemented <sup>(3)</sup>    |

| 10h          | General<br>Purpose<br>Registers |

| 1Fh          |                                 |

- Note 1: Not a physical register. See Section 4.9 "Indirect Data Addressing: INDF and FSR Registers".

- PIC10F204 only. Unimplemented on the PIC10F200 and reads as 00h.

- 3: Unimplemented, read as 00h.

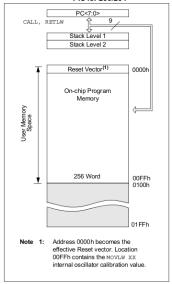

FIGURE 4-1: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC10F200/204

TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY (PIC10F200/202/204/206)

| Address            | Name     | Bit 7                         | Bit 6               | Bit 5     | Bit 4       | Bit 3      | Bit 2       | Bit 1     | Bit 0  | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

|--------------------|----------|-------------------------------|---------------------|-----------|-------------|------------|-------------|-----------|--------|----------------------------------------------|--------|

| 00h                | INDF     | Uses Cont                     | ents of FSF         | to Addre  | ss Data Mem | ory (not a | physical re | gister)   |        | xxxx xxxx                                    | 23     |

| 01h                | TMR0     | 8-bit Real-Time Clock/Counter |                     |           |             |            |             | xxxx xxxx | 29, 33 |                                              |        |

| 02h <sup>(1)</sup> | PCL      | Low-order 8 bits of PC        |                     |           |             | 1111 1111  | 22          |           |        |                                              |        |

| 03h                | STATUS   | GPWUF                         | CWUF <sup>(5)</sup> | _         | TO          | PD         | Z           | DC        | С      | 00-1 1xxx <sup>(3)</sup>                     | 19     |

| 04h                | FSR      | Indirect Da                   | ita Memory          | Address I | Pointer     |            |             |           |        | 111x xxxx                                    | 23     |

| 05h                | OSCCAL   | CAL6                          | CAL5                | CAL4      | CAL3        | CAL2       | CAL1        | CAL0      | FOSC4  | 1111 1110                                    | 21     |

| 06h                | GPIO     | _                             | _                   | _         | _           | GP3        | GP2         | GP1       | GP0    | xxxx                                         | 25     |

| 07h <sup>(4)</sup> | CMCON0   | CMPOUT                        | COUTEN              | POL       | CMPT0CS     | CMPON      | CNREF       | CPREF     | CWU    | 1111 1111                                    | 34     |

| N/A                | TRISGPIO | _                             | _                   | _         | _           | I/O Contro | Register    |           |        | 1111                                         | 37     |

| N/A                | OPTION   | GPWU                          | GPPU                | T0CS      | T0SE        | PSA        | PS2         | PS1       | PS0    | 1111 1111                                    | 20     |

$\begin{tabular}{ll} \textbf{Legend:} & -= \text{unimplemented, read as '0', } x = \text{unknown, } u = \text{unchanged, } q = \text{value depends on condition.} \\ \end{tabular}$

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.7 "Program Counter" for an explanation of how to access these bits.

- Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset

- 3: See Table 9-1 for other Reset specific values.

- 4: PIC10F204/206 only.

- 5: PIC10F204/206 only. On all other devices, this bit is reserved and should not be used.

#### REGISTER 4-1: STATUS REGISTER

| R/W-0 | R/W-0               | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |   |

|-------|---------------------|-------|-----|-----|-------|-------|-------|---|

| GPWUF | CWUF <sup>(1)</sup> | _     | TO  | PD  | Z     | DC    | С     |   |

| bit 7 |                     |       |     |     |       |       | bit 0 | 1 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| -n = Value at P | OR '1' = Bit is :                                                                                                                                                                                                                                                                                                                                          | set '0' = Bit is                                                        | cleared               | x = Bit is unknown   |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|----------------------|--|--|--|

| bit 7           | GPWUF: GPIO Reset bit<br>1 = Reset due to wake-up<br>0 = After power-up or other                                                                                                                                                                                                                                                                           | o from Sleep on pin change<br>er Reset                                  |                       |                      |  |  |  |

| bit 6           | CWUF: Comparator Wake-up on Change Flag bit <sup>(1)</sup> 1 = Reset due to wake-up from Sleep on comparator change 0 = After power-up or other Reset conditions.                                                                                                                                                                                          |                                                                         |                       |                      |  |  |  |

| bit 5           | Reserved: Do not use. U                                                                                                                                                                                                                                                                                                                                    | se of this bit may affect upw                                           | ard compatibility wit | h future products.   |  |  |  |

| bit 4           | TO: Time-out bit  1 = After power-up, CLRNDT instruction or SLEEP instruction  0 = A WDT ime-out occurred                                                                                                                                                                                                                                                  |                                                                         |                       |                      |  |  |  |

| bit 3           | PD: Power-Down bit  1 = After power-up or by the CLENDT instruction 0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                              |                                                                         |                       |                      |  |  |  |

| bit 2           |                                                                                                                                                                                                                                                                                                                                                            | netic or logic operation is ze<br>netic or logic operation is no        |                       |                      |  |  |  |

| bit 1           | DC: Digit Carry/Eorrow bit (for ADDAF and SUBNE instructions)  ADDME:  1 = A carry from the 4th low-order bit of the result occurred  0 = A carry from the 4th low-order bit of the result did not occur  SUBNE:  1 = A borrow from the 4th low-order bit of the result did not occur  O = A borrow from the 4th low-order bit of the result did not occur |                                                                         |                       |                      |  |  |  |

| bit 0           | C: Carry/Borrow bit (for A<br>ADDWF:<br>1 = A carry occurred                                                                                                                                                                                                                                                                                               | DDWF, SUBWF and RRF, RLF<br><u>SUBWF</u> :<br>1 = A borrow did not occu | RRF or RLF:           | or MSb, respectively |  |  |  |

Note 1: This bit is used on the PIC10F204/206. For code compatibility do not use this bit on the PIC10F200/202.

0 = A carry did not occur 0 = A borrow occurred

### REGISTER 4-3: OSCCAL REGISTER

| R/W-1 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | FOSC4 |

| bit 7 |       |       | •     |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 7-1

CAL<6:0>: Oscillator Calibration bits

0111111 = Maximum frequency

0000001

0000000 = Center frequency

11111111

1

1000000 = Minimum frequency

bit 0

FOSC4: INTOSC/4 Output Enable bit<sup>(1)</sup>

1 = INTOSC/4 output onto GP2

0 = GP2/T0CKI/COUT applied to GP2

Note 1: Overrides GP2/T0CKI/COUT control registers when enabled.

#### REGISTER 4-2: OPTION REGISTER

| W-1   | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|------|------|-----|-----|-----|-------|

| GPWU  | GPPU | T0CS | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7 |      |      |      |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 GPWU: Enable Wake-up on Pin Change bit (GP0, GP1, GP3)

1 = Disabled 0 = Enabled

bit 6 GPPU: Enable Weak Pull-ups bit (GP0, GP1, GP3)

1 = Disabled

0 = Enabled

bit 5 TOCS: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin (overrides TRIS on the T0CKI pin)

0 = Transition on internal instruction cycle clock, Fosc/4

bit 4 T0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on the T0CKI pin

0 = Increment on low-to-high transition on the T0CKI pin

bit 3

PSA: Prescaler Assignment bit 1 = Prescaler assigned to the WDT

0 = Prescaler assigned to Timer0

bit 2-0 PS<2:0>: Prescaler Rate Select bits

#### Rit Value Timer() Rate WDT Rate

| Dit value | milioro marc | , TIDI ING |

|-----------|--------------|------------|

| 000       | 1:2          | 1:1        |

| 001       | 1:4          | 1:2        |

| 010       | 1:8          | 1:4        |

| 011       | 1:16         | 1:8        |

| 100       | 1:32         | 1:16       |

| 101       | 1:64         | 1:32       |

| 110       | 1:128        | 1:64       |

| 111       | 1:256        | 1:128      |

# EXAMPLE 4-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

```

MOVLW 0x10 ;initialize pointer

MOVWF FSR ;to RAM

NEXT CLRF INDF ;clear INDF

;register

INCF FSR,F ;inc pointer

BTFSC FSR,4 ;all done?

GOTO NEXT ;NO, clear next

CONTINUE

: ;YES, continue

:

```